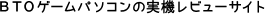

M.2スロットの罠?分岐構造と帯域制限問題を解説

投稿日:

※当ページはアフィリエイトプログラムによる収益を得ています。

高性能なNVMe SSDの普及により、M.2スロット搭載マザーボードが当たり前の時代になりましたね。

しかし、M.2スロットの構造と帯域制限について正しく理解している方は意外と少ないかもしれません。

特に、自作PCで複数のNVMe SSDやキャプチャーボード、GPUを同時運用しようとすると、思わぬ性能低下に直面することもあります。これは帯域制限が関与しています。

今回は、M.2スロットの分岐構造と帯域制限問題について詳しく解説します。

M.2スロットとPCIeレーンの仕組み

M.2スロットは、PCIeレーンと呼ばれる帯域の通り道を利用してデータ通信を行っています。

通常、CPUおよびチップセットが持つPCIeレーンを割り当て、GPU・SSD・拡張カードが分け合って使用します。

特にPCIe Gen4やGen5世代では、最大16レーン(x16)までの帯域をGPUに、4レーン(x4)をNVMe SSDに割り当てるのが一般的です。

分岐構造の罠とは?

問題は、マザーボードの設計によって、M.2スロットがCPU直結ではなくチップセット経由で接続されている場合があることです。

さらに、複数のM.2スロットを1つのPCIeレーンから分岐している設計も存在します。

このような分岐構造の場合、M.2スロット同士で帯域を奪い合うことになり、複数のSSDを同時に使用すると転送速度が低下します。

また、一部のマザーボードでは、M.2スロット使用時にSATAポートが無効化されたり、PCIe x16スロットがx8動作に制限される場合もあります。

具体例:帯域制限の発生パターン

例えば、ミドルクラスのZ790マザーボードでは、以下のような挙動が見られることがあります。

- M.2_1:CPU直結(帯域制限なし)

- M.2_2およびM.2_3:チップセット接続(PCH経由)

- M.2_4:M.2_3と帯域共有、使用時は速度が半減

さらに、M.2_2とPCIe x1スロットが帯域を共有している場合、同時使用でパフォーマンス低下することもあります。

帯域制限は避けられないのか?

高級なマザーボード(ハイエンドZ790やX670Eなど)では、ほとんどのM.2スロットがCPUに直結され、帯域制限が発生しにくい設計です。

しかし、エントリー~ミドルクラスでは、チップセット経由の分岐構造が一般的です。つまり、帯域制限を完全に避けることは困難なのです。

とはいえ、通常のゲーム用途や一般的な作業であれば、帯域制限による影響を体感する場面はほとんどありません。

大量データの同時転送や、動画編集・仮想環境構築など特殊な環境で初めて問題になります。

性能を突き詰めるなら帯域制限は回避したほうがベター

M.2スロットは非常に便利な存在ですが、接続構造と帯域制限には注意が必要です。

特に複数のNVMe SSDやPCIe拡張カードを同時に運用したい場合は、事前にマザーボードの仕様を確認しましょう。

自作PCで「なぜかSSD速度が出ない」「キャプチャーボードが認識しない」といったトラブルに遭遇した場合、M.2分岐構造と帯域制限が原因であるかもしれません。